Es de un rectificador

rectificadores de bomba de carga RF-DC en CMOS

El objetivo es que sea pequeño

Debe tener perdidas minimas

Un rectificador de bomba de

carga RF-DC de diodo de potencia ultrabaja con 32 etapas tenía un límite inferior de potencia de entrada de −31,7 dBm a un voltaje de

salida de 1,0 V.

Su pequeña área de silicio de 0,011 mm2 permite que los rectificadores RF-DC se integren en circuitos integrados de sensores.

capacitores MIM con mayor densidad de capacitancia y coloque MOSFET

de conmutación debajo de los capacitores MIM reducirá aún más el área de los rectificadores de bomba de carga RF-CC,

lo que permitirá integrarlos en circuitos integrados de sensores.

objetivos

ampliar la distancia de transmisión enfocada en la parte rectificadora del

circuito de rectena para aplicaciones de baja potencia,

o reducir el límite inferior de potencia operativa de las rectenas,

con un área de circuito rectificador lo suficientemente pequeña para ser integrado en circuitos integrados de sensores.

potencial de la wpt

, se puede construir una red de comunicación

inalámbrica al mismo tiempo para recibir y transmitir los datos detectados

Al ampliar la distancia de transmisión, se puede suministrar energía a un mayor número

de circuitos integrados de sensores en un amplio rango, como fábricas, con un solo transmisor

contexto

Se prevé billón de circuitos integrados de sensores por año gracias al desarrollo de 5G y la inteligencia artificia

metodología de diseño óptimo de rectenas y la mejora del rendimiento de los circuitos rectificadores.

problema

Las Baterias

teoria

La MWPT utiliza

ondas electromagnéticas (EM) como fuente de alimentación

Un sistema MWPT consta

principalmente de un transmisor para radiar ondas EM y un receptor con una antena receptora y un

rectificador [rectena] para capturar las ondas EM radiadas

Según la fórmula de Friis, la distancia de transmisión es inversamente proporcional al cuadrado de la

potencia recibida

su estado del arte

topología de circuito para minimizar la capacitancia de unión de los diodos para lograr una mayor eficiencia de conversión bajo la condición de impedancia de antena constante. [5]

analizo eficiencia de conversión se [6] con topología de circuito propuesta en [5]

diseño óptimo de rectenas considerando elementos parásitos generados por integración para la combinación de antena específica y rectificador en chip específico

[8] propusieron la metodología de diseño para seleccionar el rectificador óptimo de múltiples tipos para tipos de antena específicos para explorar un espacio de diseño más grande que en [5-7]

[9] propusieron una metodología para seleccionar la mejor combinación de múltiples tipos de antenas y rectificadores mediante el uso del cálculo del modelo. El análisis que cubre una gama más amplia de condiciones de diseño se puede realizar en un tiempo más corto que en [8].

En [10], se propuso una topología de circuito para cancelar el voltaje umbral conectando las compuertas de NMOS y PMOS en cada etapa de la unidad rectificadora a los terminales de salida y entrada, respectivamente, porque el voltaje umbral tiene un gran efecto en la eficiencia de conversión del rectificador en chip. Sin embargo, bajo la condición de operación de alta potencia, existe una desventaja: la corriente de fuga inversa se vuelve grande debido a que la polarización de la compuerta es excesiva.

[11] agregaron una segunda ruta de rectificación para almacenar cargas excesivas en un capacitor de almacenamiento cuando la potencia de entrada es extremadamente grande. Cuando la potencia de entrada no es suficiente, los CI de sensores se operan con la energía en el capacitor de almacenamiento almacenada de antemano. Este método logró una sensibilidad de −29,0 dBm bajo una condición de salida de 0,44 V/1,9 μA. Sin embargo, es necesario ingresar −15,4 dBm o más de antemano

[12], se propone un rectificador impulsado por oscilador LC para aumentar el voltaje de salida incluso con una potencia de entrada muy baja. En este trabajo se informa de una sensibilidad de -34,5 dBm en una condición de salida instantánea de 1,6 V/0,89 μA al suministrar un voltaje CC bajo adicional de 0,3 V.

[13], se mejoró la sensibilidad utilizando una bomba de carga (CP) RF-CC con 50 etapas de los transistores conectados a diodos más simples. Este trabajo informó que se requiere una potencia de entrada baja de -32,1 dBm para obtener el voltaje de salida de 1 V para una carga capacitiva.

[14] informaron de que se puede lograr una alta sensibilidad con solo seis etapas de rectificación aplicando autopolarización a las compuertas de los transistores rectificadores. Aunque el número de etapas no es mucho, el área se vuelve grande porque se necesitan más transistores y condensadores en el circuito de polarización. En este trabajo se informa de una sensibilidad de -30,0 dBm en una condición de salida de 1 V para una carga capacitiva.

[15], se informa que se logra una alta sensibilidad y tolerancia frente a fluctuaciones de temperatura y variaciones de ángulo de proceso conectando cinco etapas de un duplicador de voltaje con dos tipos de diodos rectificadores. Este trabajo informa que se requiere una potencia de entrada de −33,0 dBm para obtener el voltaje de salida de 1 V para una carga de 1 GΩ. Otro enfoque de diseño es adoptar un transformador en chip Figura 1. Diagrama de bloques del circuito de rectenna para MWPT. R

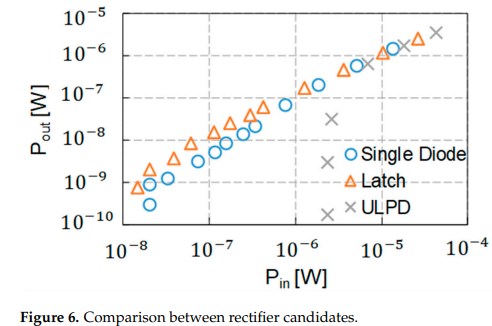

comparacion

Compara el rendimiento con trabajos anteriores en la banda de 920 MHz.

El U32 logró la mayor sensibilidad entre los rectificadores fabricados.

conclusiones

En este trabajo, un rectificador ULPD de 32 etapas en CMOS de 65 nm logró el área mínima de 0,011 mm2 y una sensibilidad de −31,7 dBm comparable a trabajos anteriores.

El diseño comenzó con la determinación de la capacitancia de un condensador de etapa tan pequeño como 100 fF para un área de circuito pequeña pero lo suficientemente grande contra una capacitancia parásita de un orden de 1 fF. Para mejorar la sensibilidad, se hicieron las siguientes dos consideraciones de diseño de disposición: (1)

los cables de metal anchos para los condensadores MIM de refuerzo anchos redujeron la resistencia parásita en las líneas de señal de RF, y (2)

una estructura de almohadilla de protección a tierra redujo la capacitancia y la resistencia parásitas. Se esperaba que un rectificador de enganche CMOS o de acoplamiento cruzado fuera el rectificador con la mayor sensibilidad con SPICE, mientras que un rectificador ULPD fue el mejor con la medición. La causa raíz de esta discrepancia deberá investigarse en trabajos futuros. Una tecnología más avanzada que proporcione a los capacitores MIM una mayor densidad de capacitancia y coloque MOSFET de conmutación debajo de los capacitores MIM reducirá aún más el área de los rectificadores de bomba de carga RF-CC, lo que permitirá integrarlos en circuitos integrados de sensores.

diseño

circuito rectificador pequeño como una alta sensibilidad.

El diseño comienza con una Suposición inicial de un capacitor suficientemente pequeño por etapa del CP RF–DC pero lo suficientemente grande como para no verse afectado por capacitancias parásitas como la capacitancia de unión y la capacitancia de torsión. El resto de los parámetros de diseño se determinan uno por uno bajo la condición de que la potencia de entrada requerida para generar 1 V en el terminal de salida del CP RF–DC se minimice.

distribucion

La Sección 2 muestra las características y esquemas de los rectificadores que componen cada etapa a optimizar.

La Sección 3 explica el flujo de optimización de la unidad rectificadora y los parámetros de circuito óptimos determinados.

La Sección 4 presenta circuitos fabricados y resultados de medición.

La Sección 5 muestra el resultado de la comparación de trabajos previos con este trabajo desde ambas perspectivas de área y sensibilidad de entrada.

La Sección 6 resume esta investigación.

circuitos rectificadores

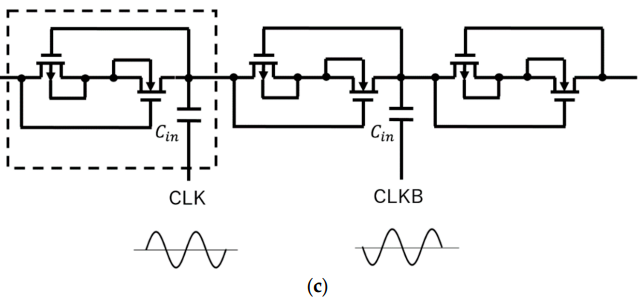

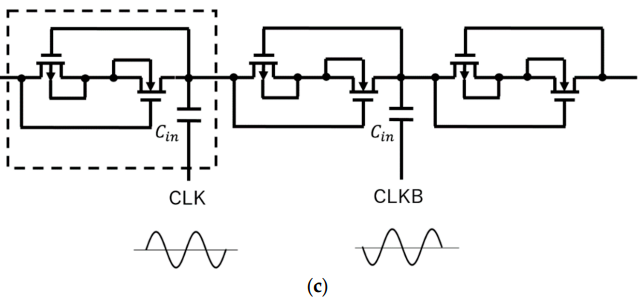

a) un rectificador de diodo único [13],

a) un rectificador de diodo único [13], (b) un rectificador de acoplamiento cruzado o de enganche CMOS [17]

(b) un rectificador de acoplamiento cruzado o de enganche CMOS [17] (c) un diodo de potencia ultrabaja (ULPD) [18].

(c) un diodo de potencia ultrabaja (ULPD) [18].funcionamiento bomba de carga

Con

CLK alto y

CLKB bajo las cargas almacenadas en el condensador Cin del lado izquierdo se transfieren al Cin del lado derecho.

Con CLK bajo y CLKB alto, las cargas almacenadas en el condensador Cin del lado derecho se transfieren al siguiente condensador.

las cargas se transfieren de uno al siguiente cada medio ciclo. aumentar el voltaje de salida

porciones encerradas por líneas discontinuas representan una etapa de los rectificadores

Asume un Cin de 100 fF, lo suficientemente para ignorar el impacto de la capacitancia parásita, como la unión PN de los transistores de conmutación y el cableado, en la eficiencia de transferencia de carga bajo una potencia de entrada baja, pero lo suficientemente pequeña como para integrarla en los circuitos integrados de sensores.

El rectificador de diodo único tiene un transistor NMOS por etapa, con un pozo P aislado y un pozo N que encierran el pozo P aislado conectados con su terminal de fuente juntos.

Debido a los NMOSFET, con terminales de drenaje que están conectados con sus propios terminales de compuerta se produce una caída de voltaje umbral por etapa, que reduce el voltaje de salida máximo alcanzable. Para

eliminar dicha caída de voltaje en los MOSFET de conmutación, se

introdujeron rectificadores de pestillo CMOS acoplados de forma cruzada.

El NMOSFET en la ruta superior se enciende fuertemente con CLK alto y CLKB bajo, mientras que el PMOSFET en la ruta superior se apaga fuertemente. el capacitor superior se carga desde la etapa anterior.

Por el contrario, el NMOSFET en la ruta inferior se apaga fuertemente con CLK alto y CLKB bajo, mientras que el PMOSFET en la ruta inferior se enciende fuertemente.

El capacitor inferior se descarga a la siguiente etapa.

para encenderse, los MOSFET pueden operar en la región lineal para eliminar la caída de voltaje umbral

Se espera que el rectificador de tipo pestillo CMOS tenga una alta eficiencia de conversión, especialmente en la operación de la región subumbral con voltajes de compuerta potenciados.

.

El pozo P aislado del NMOSFET está encerrado por el pozo N del PMOSFET

Cuatro transistores comparten el mismo pozo

DESVENTAJA se necesitan más transistores por etapa

La capacitancia parásita puede ser mayor que la del rectificador de un solo diodo

Un ULPD tiene un NMOSFET y un PMOSFET conectados en serie por etapa.

La compuerta PMOS está conectada al terminal de salida y la compuerta NMOS está conectada al terminal de entrada, lo que puede suprimir la corriente de polarización inversa mientras que la corriente de polarización directa es comparable a la del rectificador de diodo único [19]

. El pozo P aislado del NMOSFET está encerrado por el pozo N del PMOSFET. Por lo tanto, esos dos transistores comparten el mismo pozo N

Optimización

la potencia de entrada requerida para generar 1 V en el terminal de salida del CP RF–DC se minimiza con CMOS de 65 nm.

La sensibilidad del rectificador se define por la potencia de entrada para lograr 100 pW en Vout de 1 V y f de 920 MHz

en este documento. Esto da como resultado curvas Pin − Pout con diferentes condiciones de parámetros en Vout de 1 V, llama "Condición 1" óptima porque su sensibilidad es la más baja entre las tres condiciones.

asume un Cin de 100 fF, suficientemente grande para ignorar el impacto de la capacitancia parásita de un orden de 1 fF, como la unión PN de transistores de conmutación y cables en la eficiencia de transferencia de carga con baja potencia de entrada, suficientemente pequeño como para integrarlo en circuitos integrados de sensores.

parámetros del circuito se deben optimizar en términos :

(1) tipo de transistor,

(2) voltaje de umbral,

(3) ancho de compuerta,

(4) longitud de compuerta y

(5) número de etapas.

simulación SPICE [Se Realizaron pruebas]].

Se supone que la fuente de señal de entrada es una sinusoide ideal con impedancia cero para enfocarse en el rectificador sin antena.

La amplitud del voltaje de entrada Vamp se barre para variar Pin. Vout se fuerza a CC de 1 V. Pout se mide por Pin para dibujar un gráfico

Rectificador

un

rectificador de tipo latch CMOS con los parámetros

tiene la sensibilidad más alta.

l CMOS de 65 nm proporciona transistores de 1 V y 2,5 V.

Hay disponibles VTH bajo, estándar y alto para CMOS de 1 V,

Cuando el ancho total de la compuerta varía como 1,2, 10 y 20 µm, se utilizan tres combinaciones diferentes de W y nf

. Cuando se varía uno de los parámetros, los parámetros restantes se establecen con los valores óptimos

. Las curvas Pin − Pout para cada variación de parámetro .

En la Figura 5a, se utiliza Lmin de 280 nm para CMOS de 2,5 V.

La figura 5 indica que Pout se ve afectado por CMOS, VTH y W de manera más significativa que L, Cin y N, lo que sugiere que una relación W/L baja y una Cin pequeña son clave para lograr una mayor sensibilidad con una potencia de entrada baja siempre que N sea de hasta 24 o 32.

Para comparar el rendimiento de los convertidores RF-DC con diferentes circuitos de conmutación, los diodos simples y los ULPD se diseñan con los mismos parámetros de diseñ

Los resultados de SPICE para Pin − Pout se

El diseño de una etapa del rectificador de pestillo CMOS. Dos NMOSFET comparten un pozo P aislado común y cuatro transistores CMOS comparten un pozo N común.

En este diseño, los condensadores de etapa se colocan fuera de la región del transistor. Las líneas de señal de RF, como se muestra por CLK y CLKB, se enrutan con metal superior sobre los condensadores de etapa para minimizar la capacitancia parásita contra el sustrato de silicio.

Las líneas CLK/CLKB deben ser lo suficientemente anchas para tener una resistencia de cableado suficientemente pequeña. Incluso con un diseño de diseño cuidadoso, permaneció un ligero cambio en la sensibilidad.

Tenga en cuenta que el impacto de los elementos parásitos en la sensibilidad aumenta a medida que Pin disminuye.

Se realizó una

simulación adicional para investigar qué parámetro de Cpad y Rsub era crítico, como se

La Opción 1 es el caso en el que Cpad es tan bajo como el pad propuesto mientras que Rsub es tan alto como el convencional, y la

Opción 2 es el caso en el que Cpad es tan alto como el pad revisado mientras que Rsub es tan bajo como el convencional

. Debido a que la Opción 2 coincidió bien con el caso con el pad revisado, se concluye que Rsub es más crítico que Cpad.

Resultados

Se fabricaron cinco rectificadores, , en CMOS de 65 nm.

El rectificador de diodo único, el rectificador de tipo latch CMOS y el rectificador de tipo ULPD tenían un área de 240, 440 y 340 µm² por etapa, respectivamente. Si se pegaran transistores y capacitores MIM, el área de la etapa podría ser menor a 200 µm², porque el área del capacitor determina el área del circuito y el tamaño del capacitor es común para esos tres.

diagrama de bloques de la configuración de medición.

muestra su fotografía.

La potencia de entrada al pin del rectificador se calcula en función de la potencia de salida del generador de RF (PRF),

la potencia de reflexión (Pref) y la pérdida de cada uno de los conectores y cables [9].

La transformación balanceada-desbalanceada se coloca en la línea de microbanda para rectificadores porque la señal del generador de RF es una señal desbalanceada.

DEc

La sensibilidad se midió para cada rectificador a una resistencia de carga de 10 GΩ, los resultados medidos mostraron que la de los rectificadores ULPD es la más alta.

los resultados medidos mostraron que la de los rectificadores ULPD es la más alta. Para La discrepancia, se ejecutó una lista de conexiones más detallada que incluye elementos parásitos en líneas de microcinta y cables de unión, Lms y Cms representan la inductancia parásita y la capacitancia parásita de la línea de microcinta, respectivamente. La simulación SPICE se realizó con diferentes valores para Lms y Cms dependiendo de la longitud de la línea de microcinta debido a que la longitud de la línea de microcinta en la placa de evaluación varía según el rectificador.

La inductancia parásita del cable de unión LBW se estima en 8 nH y la capacitancia parásita de la almohadilla de unión Cpad es de 200 fF.

En esta simulación SPICE, se consideraron los efectos de la capacitancia parásita del cableado, la resistencia parásita y los diodos parásitos del transistor.

compara Pout vs. Pin y η vs. Pin bajo la condición de voltaje de salida Vout = 1 V.

Los resultados medidos y simulados concuerdan bien para Pin > 100 µW o Pout > 10 µW.

Por otro lado, los puntos de partida en los que las pendientes de Pout − Pin se vuelven más pronunciadas son diferentes entre los medidos y los simulados, especialmente en rectificadores de tipo latch y de diodo único. No pudimos identificar la causa raíz de la degradación. Será necesario investigarla en el futuro para reducir el límite inferior de la potencia de entrada.

Se logró una sensibilidad de −31,7 dBm con 0,011 mm2 U32.

Una causa potencial de la discrepancia en las curvas Pin - Pout en la región de baja potencia es La impedancia de entrada de los rectificadores varía ampliamente con la potencia de entrada,

RR y CR son resistencia de entrada y capacitancia equivalentes, cuando la impedancia de entrada se expresa mediante un circuito RC en paralelo. En la región de alta potencia de entrada, Zin se vuelve baja porque CR se vuelve grande y RR se vuelve bajo.

En la región de baja potencia de entrada, Zin se vuelve alta porque CR se vuelve grande y RR se vuelve alto. cuando Pin se barre en un amplio rango de potencia, la impedancia de entrada del rectificador varía en gran medida. Como resultado, las curvas Pin - Pout se midieron sin ningún circuito de adaptación en lugar de reemplazar el circuito de adaptación por Pin repetidamente.

En una condición de baja potencia de entrada, Zin está lejos de la impedancia característica de los cables coaxiales, lo que resulta en una gran reflexión de potencia.

la relación entre la potencia de entrada en el rectificador Pin y la potencia de salida del generador de potencia de RF Pin-ic depende de la potencia de reflexión Pref-ic.

A medida que aumenta la falta de coincidencia en la impedancia en la interfaz entre el conector y el rectificador, especialmente en la región de baja potencia, Pin/Pin-ic disminuye significativamente. La

muestra la relación entre Pin−ic, Pre f−ic y Pin de los casos. Debido a que la resolución de potencia del analizador de espectro utilizado en esta investigación es de 0,1 dB, los parámetros de pérdida extraídos deben tener una resolución de 0,1 dB. Por lo tanto, puede producirse la discrepancia entre la simulación SPICE y los resultados de la medición en la región de baja potencia.

Una sensibilidad esperada de −31,7 dBm se puede reducir a −29,6 dBm cuando todos los parámetros de pérdida están en el peor de los casos.

Con CLK alto y CLKB bajo las cargas almacenadas en el condensador Cin del lado izquierdo se transfieren al Cin del lado derecho.

Con CLK alto y CLKB bajo las cargas almacenadas en el condensador Cin del lado izquierdo se transfieren al Cin del lado derecho.  Debido a los NMOSFET, con terminales de drenaje que están conectados con sus propios terminales de compuerta se produce una caída de voltaje umbral por etapa, que reduce el voltaje de salida máximo alcanzable. Para eliminar dicha caída de voltaje en los MOSFET de conmutación, se introdujeron rectificadores de pestillo CMOS acoplados de forma cruzada.

Debido a los NMOSFET, con terminales de drenaje que están conectados con sus propios terminales de compuerta se produce una caída de voltaje umbral por etapa, que reduce el voltaje de salida máximo alcanzable. Para eliminar dicha caída de voltaje en los MOSFET de conmutación, se introdujeron rectificadores de pestillo CMOS acoplados de forma cruzada.

No hay comentarios.:

Publicar un comentario