Contexto

Aumento de dispositivos IoT y comunicacion inalambrica

Los sistemas inalámbricos sin batería generan su voltaje

de alimentación a partir de la señal de RF entrante . Los convertidores de RF a CC

convencionales solo pueden funcionar con un PCE alto a un valor específico.

, presentamos un multiplicador de tensión pasivo (MV) reconfigurable, que se adapta según la intensidad de la señal de RF entrante para mantener la tensión de CC requerida con un alto PCE a partir de la potencia de entrada disponible

,Proponemos una topología reconfigurable compatible con CMOS estándar, fácilmente ajustable a diversos niveles de potencia y que mantiene su eficiencia en un rango de potencia de entrada más amplio.

Proponemos utilizar un rectificador reconfigurable como elemento central en las etapas variables de los Multiplicadores de voltaje (VM). Gracias al mecanismo de reconfiguración, se logra un PCE alto incluso con un número creciente de etapas y condiciones de potencia de entrada variables. El número de etapas también se puede modificar para generar la potencia necesaria. Al seleccionar la mejor topología de VM, se puede lograr la mayor tensión de CC de salida posible con el mayor PCE posible

prototipo en un proceso CMOS estándar de 0,35 µm, operando a 13,56 MHz con una carga de 2 kΩ

multiplicador de voltaje presentado busca

maximizar la eficiencia de conversión de potencia (PCE)

la gran variabilidad en la potencia disponible en la entrada provoca una gran variabilidad en la tensión de CC rectificada en la salida, particularmente

El elemento central del multiplicador de tensión produce un PCE pico del 76 % con la topología de acoplamiento cruzado a baja potencia de entrada, mientras que la topología híbrida proporciona un PCE del 70 % a mayor potencia de entrada.

estructura paper

La Sección II ofrece un breve resumen de las multiplicador de tensión pasivo de última generación para bajo consumo de energía.

La Sección III presenta los detalles de implementación y los principios operativos de lamultiplicador de tensión pasivo propuesta.

La Sección IV incluye los resultados de las mediciones y las métricas de rendimiento, seguidas de las conclusiones.

estado del arte

La mayoría de los esfuerzos para aumentar la eficiencia de conversión de

potencia (PCE) de los dispositivos inalámbricos se centran en el bloque de

conversión de RF a CC [3].

se requieren duplicadores o multiplicadores

de tensión para suministrar la tensión de CC necesaria a costa de un PCE

más bajo [4], [5]

s, que

requieren un rango dinámico de potencia de entrada [6]

los investigadores han intentado recientemente abordar problemas En el rango de baja potencia de entrada con nuevos rectificadores y duplicadores reconfigurables [8]-[12],

En [6] se realizó una comparación de algunos de los VM más populares, incluyendo el VM Dickson (DVM) con diodos Schottky, transistores regulares, nativos y de bajo umbral, diodos de ultra baja potencia (ULPD) y el VM de acoplamiento cruzado (CCVM )

todas las topologías se migran al mismo proceso de fabricación, se ajustan a las mismas especificaciones objetivo y se analizan con el mismo conjunto de restricciones de entrada.

los cambios en la potencia de entrada afectan considerablemente el PCE de la mayoría de los VM, que solo son adecuados para un nivel de potencia específico.

teoria

Topologias de multiplicador de voltaje

[12], las topologías híbridas presentan comportamientos y resultados numéricos similares para el PCE en el rango medido.

La topología de cuatro interruptores (ALLS) presenta el PCE más alto en el rango de baja potencia,

mientras que la topología de cuatro diodos (ALL-D) presenta el PCE más bajo en todo el rango de potencia medido.

a bajo nivel de potencia, los interruptores PMOS degradan ligeramente el PCE de ND-PS.

en la práctica, los dispositivos semiconductores, como interruptores y diodos, presentan tensiones de caída,

Otra causa de las pérdidas es la energía acumulada en los condensadores parásitos.

un transistor conectado a un interruptor opera con mayor eficiencia que un transistor conectado a un diodo cuando la amplitud de la señal entrante, 𝑉𝑎, es inferior al nivel de voltaje umbral

En estructuras en cascada, la 𝑉𝑡ℎ de los transistores aumenta debido al efecto cuerpo, un aumento en la tensión fuente-cuerpo, 𝑉𝑠b, que afecta directamente la tensión de caída de los interruptores y transistores conectados a diodos.

El aumento de la tensión de caída reduce la conductividad de los transistores, lo que conlleva un aumento en la resistencia de salida y, a su vez, disminuye Vout. Un valor mayor de N conlleva una mayor pérdida de potencia debido a un mayor 𝑉𝑠b. Por otro lado, una VM con menos etapas podría no generar la 𝑉𝑂ut requerida. Por lo tanto, existe una compensación que debe resolverse mediante un proceso de optimización. Particularmente en aplicaciones inalámbricas móviles, un mecanismo de configuración es útil para ajustar Vout según la intensidad variable de la señal de entrada.

el diseñador debe prestar especial atención en el rango de frecuencias más altas, en el rango de GHz, mediante la instalación de un circuito de adaptación de impedancia reconfigurable entre el VM y la antena/bobina

incluso con la misma potencia de entrada, el voltaje de entrada puede ser diferente debido a estos factores.

Los multiplicadores de voltaje, por definición, multiplican el voltaje de entrada en la salida. Sin embargo, la potencia de entrada también afecta el rendimiento del VM y se debe considerar junto con el voltaje de entrada. La naturaleza no lineal de la impedancia de entrada impide extraer una relación directa entre la potencia de entrada y el voltaje de salida.

Funcionamiento

reconfiguración

entre cuatro tipos conocidos de rectificadores: rectificadores de puente,

de acoplamiento, cruzado e híbridos

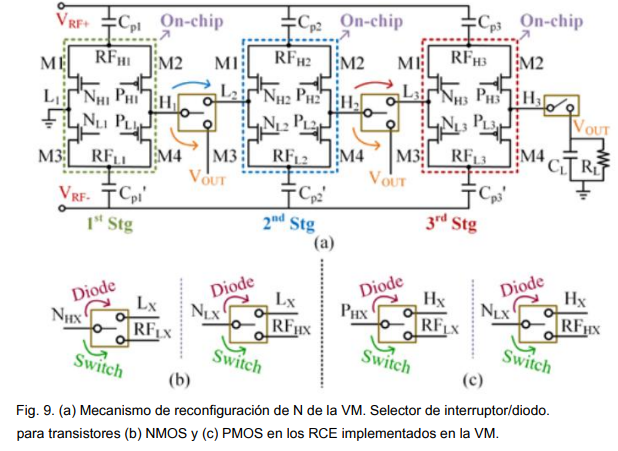

La reconfiguración se realiza modificando los transistores de interruptor a diodo y viceversa mediante la configuración sus conexiones de compuerta. como un elemento central reconfigurable (RCE) en un RVM para lograr un alto PCE a diferente niveles de potencia de entrada.

Decidimos

eliminar algunas de estas topologías Para reducir la complejidad de conmutación del sistema, especialmente al implementar varias etapas en un RVM completamente automático Optamos por

implementar el esquema de reconfiguración únicamente con diodos NMOS e interruptores PMOS (ND-PS) híbridos y topologías ALL-S Diseño

i) La topología ALL-D no tiene un rendimiento competitivo en el rango de interés, hasta varios mW.

ii) Dado que la topología ALL-S tiene el PCE más alto en el rango de potencia de entrada baja, es la elección natural para este rango.

iii) Aunque las topologías híbridas tienen un rendimiento similar, la topología NDPS logra un PCE ligeramente más alto que el de la topología NS-PD en el rango de potencia de entrada más alto

, la topología NS-PD funciona ligeramente mejor en el nivel de entrada bajo por menor voltaje de caída de los transistores NMOS (𝑉𝑉𝑡𝑡ℎ𝑛𝑛) conectados a diodos que los transistores PMOS (𝑉𝑉𝑡𝑡ℎ𝑝𝑝) conectados a diodos.

Como ALL-S se encargará de la región de baja potencia, podemos ignorar la degradación PCE de NDPS debido a los conmutadores PMOS en este rango y elegir la topología NDPS para el rango de alta potencia

el voltaje de CC de salida del multiplicador es directamente proporcional al número de etapa y se calcula mediante

N es el número de etapa y 𝑉a 𝑎 es la amplitud de la señal de entrada

N es el número de etapa y 𝑉a 𝑎 es la amplitud de la señal de entrada

donde ω = 2πf, la frecuencia angular.

ndo VRF+ es positivo, en las configuraciones ND-PS y ALLS, los transistores M2 y M3 están activados y los transistores M1 y M4 están desactivados. Mientras que los transistores M2 forman un interruptor en ambas topologías, el transistor M3 es un interruptor en la topología ALL-S y un diodo en la topología ND-

ndo VRF+ es positivo, en las configuraciones ND-PS y ALLS, los transistores M2 y M3 están activados y los transistores M1 y M4 están desactivados. Mientras que los transistores M2 forman un interruptor en ambas topologías, el transistor M3 es un interruptor en la topología ALL-S y un diodo en la topología ND-. En el semiciclo positivo, la carga fluye de Cp1 a CL a través de M2. De forma similar, cuando VRF- es positivo en el semiciclo negativo, los transistores M1 y M4 están activados y los transistores M2 y M3 están desactivados. Mientras que los transistores M4 forman un interruptor en ambas topologías, el transistor M1 forma un interruptor en la topología ALL-S y un diodo en la topología ND-

. En el semiciclo negativo, la carga fluye de

CP1 a CL a través de

Donde 𝑉DR_ND es la tensión de caída del transistor NMOS conectado al diodo y 𝑉DR_𝑃s es la tensión de caída del interruptor PMOS. Con la topología ALL-S, la tensión de CC de salida de un elemento central de una sola etapa es:

Donde 𝑉DR_ND es la tensión de caída del transistor NMOS conectado al diodo y 𝑉DR_𝑃s es la tensión de caída del interruptor PMOS. Con la topología ALL-S, la tensión de CC de salida de un elemento central de una sola etapa es: Donde 𝑉DR_NS es la tensión de caída del interruptor NMOS. Los valores transitorios de 𝑉DR_ND, 𝑉DR_NS y 𝑉DR_PS dependen de la tensión de entrada y, a su vez, de la región de operación de los transistores, lo que determina el PCE del VM. Las tensiones internas, nodos 1 y 2 se generan en la compuerta de cada interruptor. Dado que los interruptores son bidireccionales, a diferencia de los diodos, las corrientes inversa y directa de los transistores generan una tensión de modo común en los nodos etiquetados. La tensión de modo común es la combinación de CC de las tensiones de los nodos 1 y 2 y es cercana a la mitad de la tensión de salida rectificada. La tensión de modo común en la compuerta de los transistores conectados al interruptor reduce la tensión umbral efectiva de estos transistores

Donde 𝑉DR_NS es la tensión de caída del interruptor NMOS. Los valores transitorios de 𝑉DR_ND, 𝑉DR_NS y 𝑉DR_PS dependen de la tensión de entrada y, a su vez, de la región de operación de los transistores, lo que determina el PCE del VM. Las tensiones internas, nodos 1 y 2 se generan en la compuerta de cada interruptor. Dado que los interruptores son bidireccionales, a diferencia de los diodos, las corrientes inversa y directa de los transistores generan una tensión de modo común en los nodos etiquetados. La tensión de modo común es la combinación de CC de las tensiones de los nodos 1 y 2 y es cercana a la mitad de la tensión de salida rectificada. La tensión de modo común en la compuerta de los transistores conectados al interruptor reduce la tensión umbral efectiva de estos transistores𝑉DR_PS y 𝑉DR_NS se vuelven inferiores a 𝑉𝑡ℎ. Por otro lado, el voltaje umbral efectivo para un transistor conectado a un diodo permanece en 𝑉𝑡ℎ.

Una vez que la amplitud de la señal de entrada, 𝑉𝑎, excede el voltaje umbral y cuando 𝑉out > 𝑉𝑎 en el ciclo periódico, el transistor conectado a un interruptor conduce en la dirección inversa. En este caso, un 𝑉𝑎 mayor causa la mayor fuga y el PCE menor

La relación de aspecto de todos los transistores en el elemento central es la misma

Los condensadores de bombeo son de 1 nF y la capacitancia de carga es de 100 nF en el VM. Al conectar en cascada los RCE, un RVM de N etapas genera un voltaje de salida rectificado como [12]

cuando se reconfigura como VM ND-PS y,

cuando se reconfigura como VM ND-PS y, cuando se reconfigura con ALL-S VM

cuando se reconfigura con ALL-S VMPor defecto, el VM puede arrancar con todas las etapas, y el número de etapas se puede ajustar según la potencia de la señal entrante mediante un controlador sencillo.

La disposición simétrica de los condensadores y los RCE ayuda a excitar los diodos/interruptores con la misma señal de entrada. Esta disposición reduce los armónicos reflejados, que podrían causar un desequilibrio de corriente en el VM. Otro punto importante es la variación de la impedancia de entrada del VM con N, la topología seleccionada y la potencia de entrada.

Hemos analizado el PCE para RVM con una, dos y tres etapas a 13,56 MHz bajo una carga de 2 kΩ. El rendimiento PCE de las máquinas virtuales (VM) con hasta tres etapas

Las mejoras PCE con los RCE en las RVM se muestran mediante flechas añadidas a las figuras, en comparación con una topología fija de rectificadores ALL-S y ND-PS.

Las mejoras PCE con los RCE en las RVM se muestran mediante flechas añadidas a las figuras, en comparación con una topología fija de rectificadores ALL-S y ND-PS. la mejora en el nivel de baja potencia mejora significativamente el alcance de lectura de los dispositivos móviles.

La (VM) debería arrancar con un RCE tipo ALL-S como medida de precaución ante la falta de potencia para que el tipo ND-PS funcione eficientemente. El controlador puede cambiar la topología a ND-PS cuando la potencia recibida sea lo suficientemente alta. También analizamos la tensión de CC de salida de las VM frente a la tensión y la potencia de entrada.

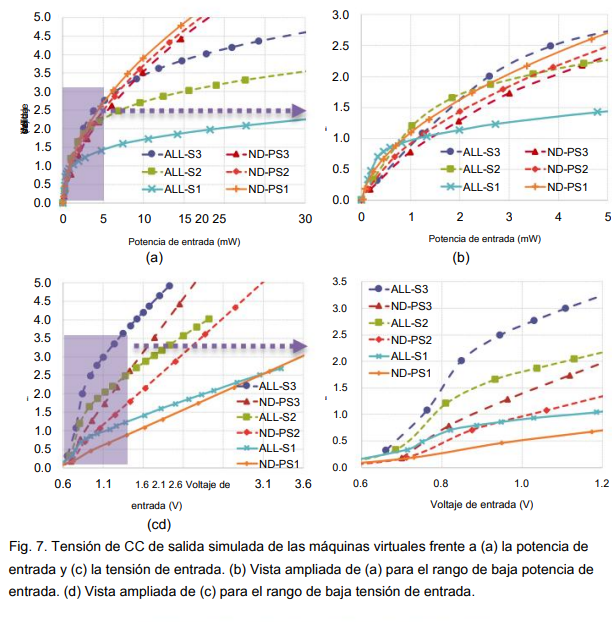

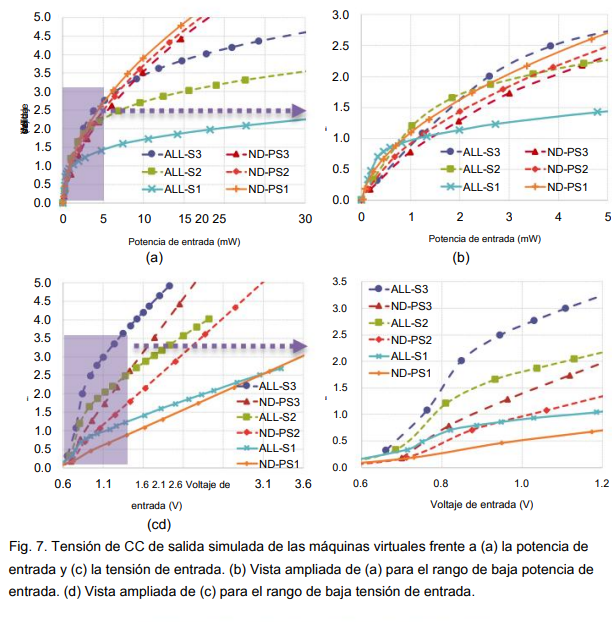

La Fig. 7a muestra la tensión de salida con la potencia de entrada variable, mientras que la Fig. 7b amplía el rango de baja tensión. La Fig. 7c muestra las tensiones de salida frente a la tensión de entrada, mientras que la Fig. 7d amplía el rango de baja tensión de entrada

La Fig. 7a muestra la tensión de salida con la potencia de entrada variable, mientras que la Fig. 7b amplía el rango de baja tensión. La Fig. 7c muestra las tensiones de salida frente a la tensión de entrada, mientras que la Fig. 7d amplía el rango de baja tensión de entrada El comportamiento del voltaje de salida al variar la potencia presenta características diferentes a las del comportamiento al variar el voltaje de entrada, debido a la naturaleza compleja de la impedancia de entrada, que se ve afectada por N.

para aumentar aún más el voltaje de entrada, necesitamos aumentar significativamente la potencia de entrada; por lo tanto, preferimos mantener la potencia de entrada en un rango inferior a 40 mW, lo que provocó que los voltajes de entrada se mantuvieran en 1,8 V para ALL-S3 y 2,5 V para ALL-S2

resultados

El RVM se fabricó en el proceso CMOS estándar de 0,35 µm de TSMC.

muestra la configuración de la medición y la micrografía del chip del elemento central. La reconfiguración del VM se realizó a nivel de placa,

. Las mediciones se realizaron con un analizador vectorial de redes (Rohde & Schwartz, ZVB 4). La potencia a la entrada del VM se estimó calculando las pérdidas de potencia a partir del parámetro S11 medido y restando estas pérdidas de la potencia suministrada desde el puerto de 50 Ω del analizador vectorial de redes. Dado que la potencia calculada a la entrada del VM sería suficiente para nuestro análisis, optamos por dejar

el diseño de una red de adaptación de impedancias fuera del alcance de este informe. Sin embargo, u

n varactor integrado sería una opción adecuada en un enlace inductivo a 13,56 MHz. El voltaje de entrada de CA generado por el analizador de redes vectoriales (VNA) en un solo tono se establece al mínimo (en el VNA ZVB4, el rango mínimo es de 2 Hz), y l

a frecuencia central se establece en 13,56 MHz. Se conecta una carga de 2 kΩ en paralelo con un condensador de 100 nF a la salida del multiplicador. Metodologia

Para aplicar una señal de CA de un solo tono consiste en aumentar el tamaño del paso de barrido de frecuencia. El VNA barre varias frecuencias paso a paso.

La duración del paso se puede seleccionar lo suficientemente larga como para obtener el resultado de la medición a la frecuencia establecida.

Las mediciones de todos los VM se realizaron en las mismas condiciones.

El mecanismo de reconfiguración del RCE, que cambia entre las topologías ALL-S y ND-PS, se realizó controlando la polarización de las puertas de los transistores en los RCE.

Se modificó externamente la polarización de las puertas en la PCB, Las puertas de los transistores se conectan al pin central del conector y, al cambiar la posición del puente, el transistor se configura como un diodo o un interruptor. El otro mecanismo de reconfiguración, que modifica el nivel de voltaje de salida, se implementó aumentando el número de etapas del convertidor de RF a CC mediante la conexión en cascada de los RCE,

Se midió el voltaje de salida y el PCE de los VM con una potencia de entrada de hasta 14 dBm (25,11 mW), que es el nivel máximo de potencia que el VNA ZVB4 puede suministrar. La Fig. 10 presenta el rendimiento PCE medido de los VM con una, dos y tres etapas, respectivamente, variando la potencia de entrada. En el rango de baja potencia, los RVM operan con topología ALLS, que presenta un PCE de ⁓76 %. Dado que el circuito necesita mayor potencia cuando N aumenta, el punto pico de PCE cambia con la potencia de entrada variable.

Como hemos discutido en la Sección III, este alto PCE se logra debido a un mayor voltaje de sobremarcha (𝑉𝐺 − 𝑉𝑡ℎ ), menor 𝑅𝑅𝑜𝑜𝑜𝑜 , lo que a su vez reduce la potencia disipada en los conmutadores. Además, el aumento de 𝑉s con el aumento de N no afecta gravemente al PCE de la topología ALLS porque la señal de modo común, como nodo 1 y nodo 2 en la compuerta de los conmutadores, aumenta con la potencia entrante y el voltaje de sobremarcha efectivo aún permanece relativamente alto para soportar el alto PCE ⁓76%.

Como la potencia de entrada aplicada está limitada por la potencia que puede proporcionar el VNA, en particular para el VM de tres etapas, no se pudo realizar la medición para niveles de potencia más altos como en la simulación.

las simulaciones y las mediciones concuerdan bien.

Los voltajes de CC de salida medidos con potencia de CA de entrada variable

. En el rango de potencia baja, la topología

ALLS con una sola etapa alcanza la 𝑉𝑂ut más alta hasta que la potencia de entrada es de 1 mW. Desde este punto hasta 3 mW, la misma topología con dos etapas tiene la 𝑉𝑂ut más alta. La topología ALL-S con 3 etapas genera la 𝑉𝑂ut más alta; Sin embargo, en la simulación se observó que la salida del ND-PS de 3 etapas supera la salida del ALL-S de 3 etapas en el rango de potencia superior.

Las tensiones transitorias de salida de CC medidas de los múltiplos de tensión s

. Se aplican tensiones de entrada de

0,75 V pico y 1,75 V pico a 13,56 MHz y la carga de salida se establece en 2 kΩ. Los valores transitorios medidos reflejan un comportamiento similar de las tensiones de salida, como se muestra en las Figs. 11c y 11d. La Tabla I compara el VM propuesto con los descritos en la literatura.

1. Tecnologías Empleadas

- CMOS estándar de 0.35 µm: La implementación del circuito se realizó en esta tecnología para garantizar compatibilidad con procesos convencionales y mejorar la integración con otros sistemas electrónicos.

- Conversión RF-DC: Se emplea un convertidor que transforma la energía de radiofrecuencia en corriente continua.

- Reconfiguración Dinámica: La topología del multiplicador de voltaje se ajusta automáticamente en función de la potencia de la señal RF entrante para maximizar la eficiencia de conversión de potencia (PCE).

- Frecuencia de Operación de 13.56 MHz: La elección de esta frecuencia está alineada con aplicaciones RFID y WPT (Wireless Power Transfer).

2. Componentes Electrónicos y sus Usos

(a) Diodos y Transistores MOSFET

- Se utilizan diodos y transistores MOSFET en distintas configuraciones para actuar como rectificadores y conmutadores.

- Topologías Utilizadas:

- ND-PS (NMOS diodos + PMOS switches): Mejora la conversión a voltajes más altos.

- ALL-S (Switches en todas las posiciones): Optimiza la eficiencia en bajos niveles de entrada.

- Funcionamiento:

- Los transistores pueden alternar entre modo conmutador (switch) y modo diodo dependiendo de la configuración de sus compuertas.

- En la topología ALL-S, los transistores operan como interruptores bidireccionales, mientras que en ND-PS, los NMOS se configuran como diodos y los PMOS como switches.

(b) Condensadores de Bombeo y de Carga

- Condensadores de Bombeo (1 nF): Almacenan y transfieren carga en cada ciclo de conmutación del multiplicador de voltaje.

- Condensador de Carga (100 nF): Suaviza la salida de voltaje y reduce la ondulación.

(c) Carga Resistiva (2 kΩ)

- Se emplea una resistencia de carga de 2 kΩ en la salida del multiplicador de voltaje para simular condiciones de operación reales.

(d) Circuitos de Reconfiguración

- Se utiliza una red de control de compuertas para cambiar dinámicamente entre las topologías ALL-S y ND-PS, dependiendo del nivel de potencia de entrada.

3. Aportaciones del Trabajo

- Reconfigurabilidad Dinámica: A diferencia de los multiplicadores convencionales que solo funcionan de manera óptima en un rango específico de potencia de entrada, este diseño cambia de configuración para mantener una alta eficiencia en distintas condiciones.

- Alta Eficiencia:

- 76% de PCE en baja potencia con la topología ALL-S.

- 70% de PCE en alta potencia con la topología ND-PS.

- Optimización del Número de Etapas:

- Se ajusta el número de etapas del multiplicador de voltaje según la potencia de entrada, evitando pérdidas innecesarias.

- Compatibilidad con RFID e IoT:

- Ideal para dispositivos de bajo consumo energético que operan sin batería, como sensores IoT inalámbricos.

Conclusión

Este trabajo introduce un multiplicador de voltaje pasivo reconfigurable, diseñado en tecnología CMOS de 0.35 µm, con una eficiencia mejorada gracias a la conmutación entre diferentes topologías rectificadoras. Su principal ventaja es la capacidad de adaptarse dinámicamente a la potencia de la señal RF de entrada, lo que lo hace ideal para recolección de energía en sistemas IoT y RFID. 🚀

ndo VRF+ es positivo, en las configuraciones ND-PS y ALLS, los transistores M2 y M3 están activados y los transistores M1 y M4 están desactivados. Mientras que los transistores M2 forman un interruptor en ambas topologías, el transistor M3 es un interruptor en la topología ALL-S y un diodo en la topología ND-

ndo VRF+ es positivo, en las configuraciones ND-PS y ALLS, los transistores M2 y M3 están activados y los transistores M1 y M4 están desactivados. Mientras que los transistores M2 forman un interruptor en ambas topologías, el transistor M3 es un interruptor en la topología ALL-S y un diodo en la topología ND- La Fig. 7a muestra la tensión de salida con la potencia de entrada variable, mientras que la Fig. 7b amplía el rango de baja tensión. La Fig. 7c muestra las tensiones de salida frente a la tensión de entrada, mientras que la Fig. 7d amplía el rango de baja tensión de entrada

La Fig. 7a muestra la tensión de salida con la potencia de entrada variable, mientras que la Fig. 7b amplía el rango de baja tensión. La Fig. 7c muestra las tensiones de salida frente a la tensión de entrada, mientras que la Fig. 7d amplía el rango de baja tensión de entrada

No hay comentarios.:

Publicar un comentario